ZA9L1 Overview

Key Specifications

Pins: 256

Max Frequency: 200 MHz

Max Operating Temp: 85 °C

Min Operating Temp: -40 °C

Description

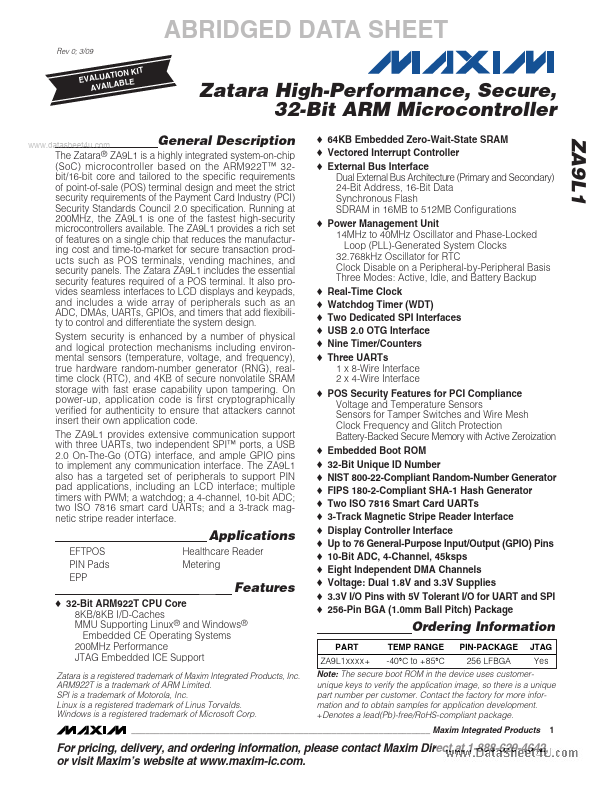

64KB Embedded Zero-Wait-State SRAM - Vectored Interrupt Controller - External Bus Interface Dual External Bus Architecture (Primary and Secondary) 24-Bit Address, 16-Bit Data Synchronous Flash SDRAM in 16MB to 512MB Configurations - Power Management Unit 14MHz to 40MHz Oscillator and Phase-Locked Loop (PLL)-Generated System Clocks 32.768kHz Oscillator for RTC Clock Disable on a Peripheral-by-Peripheral Basis Three Modes: Active, Idle, and Battery Backup - Real-Time Clock - Watchdog Timer (WDT) - Two Dedicated SPI Interfaces - USB 2.0 OTG Interface - Nine Timer/Counters - Three UARTs 1 x 8-Wire Interface 2 x 4-Wire Interface - POS Security Features for PCI Compliance Voltage and Temperature Sensors Sensors for Tamper Switches and Wire Mesh Clock Frequency and Glitch Protection Battery-Backed Secure Memory with Active Zeroization - - - - - - - - - - - - - Embedded Boot ROM 32-Bit Unique ID Number NIST 800-22-Compliant Random-Number Generator FIPS 180-2-Compliant SHA-1 Hash Generator Two ISO 7816 Smart Card UARTs 3-Track Magnetic Stripe Reader Interface Display Controller Interface Up to 76 General-Purpose Input/Output (GPIO) Pins 10-Bit ADC, 4-Channel, 45ksps Eight Independent DMA Channels Voltage: Dual 1.8V and 3.3V Supplies 3.3V I/O Pins with 5V Tolerant I/O for UART and SPI 256-Pin BGA (1.0mm Ball Pitch) Package ZA9L1 The Zatara® ZA9L1 is a highly integrated system-on-chip (SoC) microcontroller based on the ARM922T™ 32bit/16-bit core and tailored to the specific requirements of point-of-sale (POS) terminal design and meet the strict security requirements of the Payment Card Industry (PCI) Security Standards Council 2.0 specification. Running at 200MHz, the ZA9L1 is one of the fastest high-security microcontrollers available.

Key Features

- Running at 200MHz, the ZA9L1 is one of the fastest high-security microcontrollers available

- The ZA9L1 provides a ric